全球能源互联网核心节点赋能者-BASiC Semiconductor基本半导体之一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

基本半导体(BASiC Semiconductor)的 1200V SiC MOSFET 大功率模块与青铜剑技术(Bronze Technologies)的配套智能驱动板的数据手册,进行固态变压器(SST, Solid State Transformer)的系统建模、仿真与架构优化,是一个高度契合当前大功率电力电子前沿的工程实践。

固态变压器通常采用三级架构:高压交流整流级(AC/DC) 、高频隔离级(DC/DC,如DAB或LLC)和低压逆变级(DC/AC) 。为了最大化 SiC 模块的性能并确保系统鲁棒性,以下是全流程建模、仿真与优化指南:

一、 SST 硬件选型与功率单元匹配

首先,根据数据手册的物理封装和电气特性,为 SST 的不同级构建“即插即用”的标准功率单元(Power Cell):

高压/中压侧 (MV AC → MV DC):如级联H桥 (CHB) 或 MMC 单元

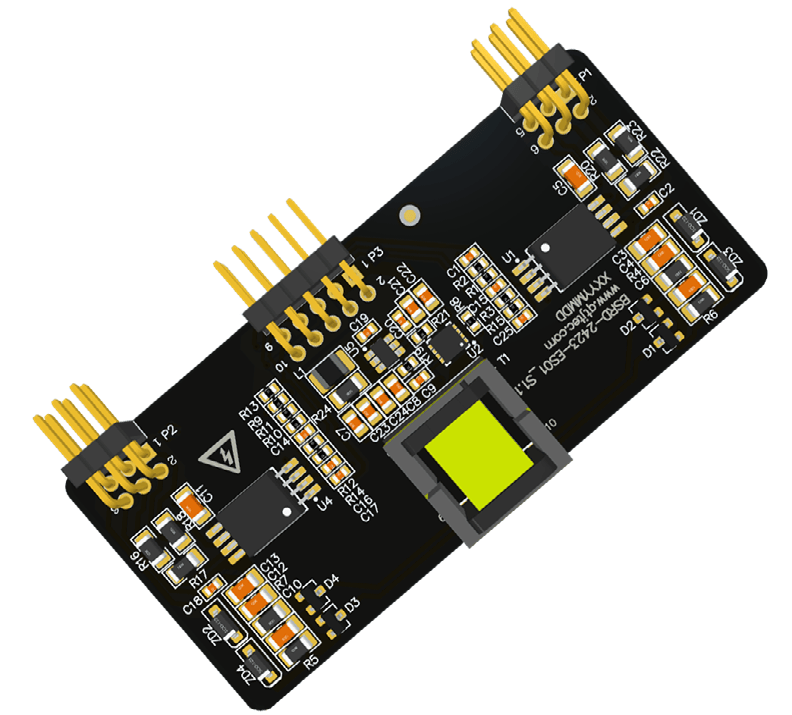

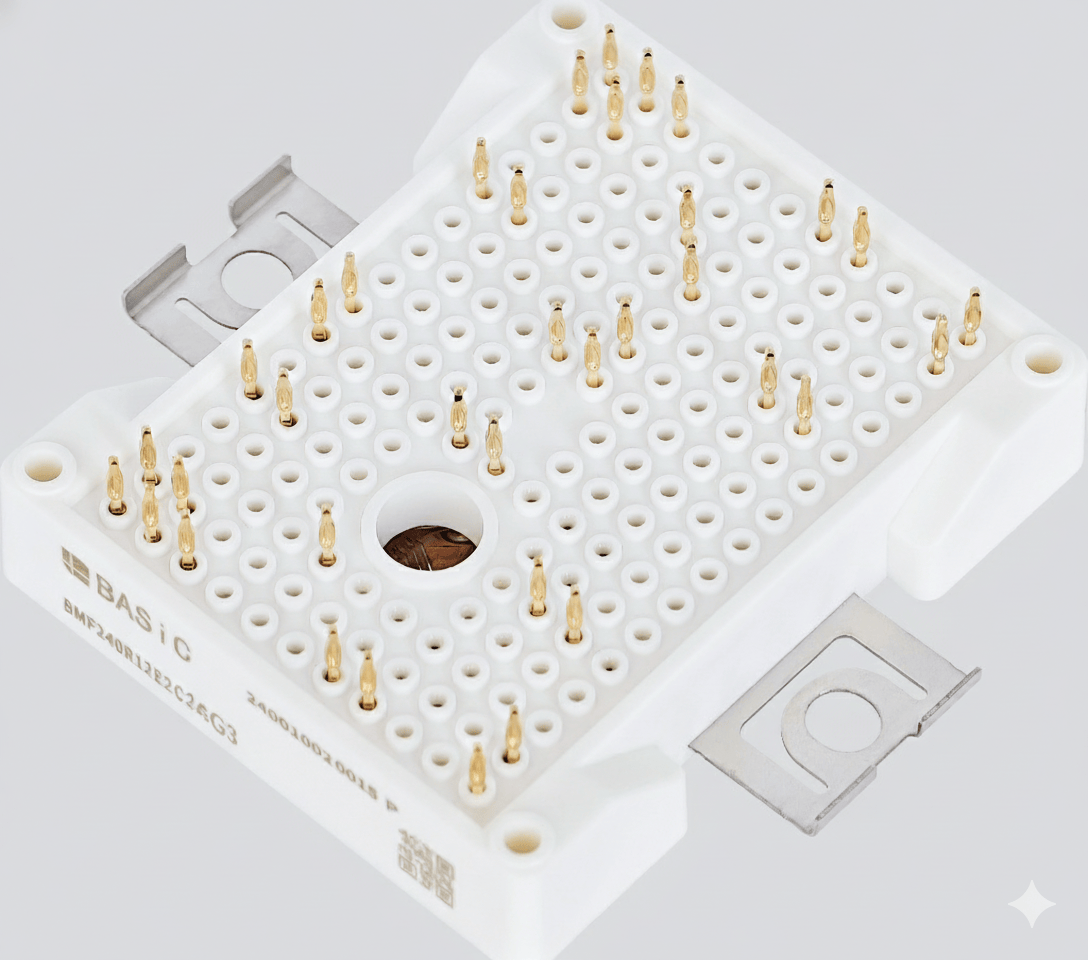

- 硬件组合: BMF240R12E2G3 (1200V/240A) + 2CD0210T12x0 双通道驱动板。

- 匹配逻辑: 高压侧通常采用多模块串联,单模块电流需求较小。240A模块栅极电荷小(QG=492nC),驱动板 2W/±10A 的能力足以支持其在极高频率下运行(理论支持 >100kHz),且驱动内置的米勒钳位能有效防止多级串联架构中极高 dv/dt 引起的串扰直通。

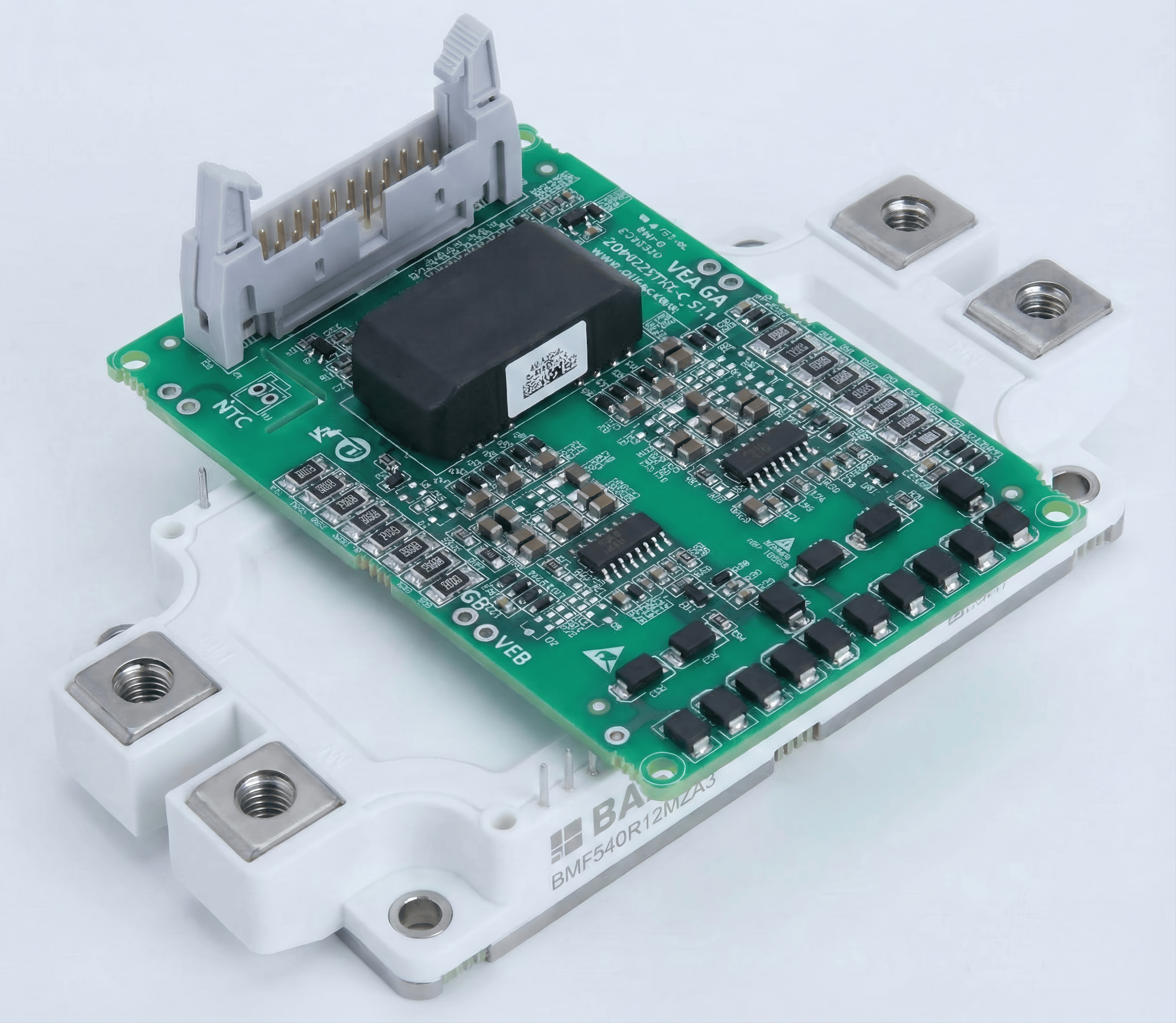

高频隔离核心级 (MV DC → LV DC):大功率双有源桥 (DAB) 单元

- 硬件组合 A(EconoDual封装): BMF540R12MZA3 (540A) + 2CP0225Txx-AB 驱动板 (±25A)。

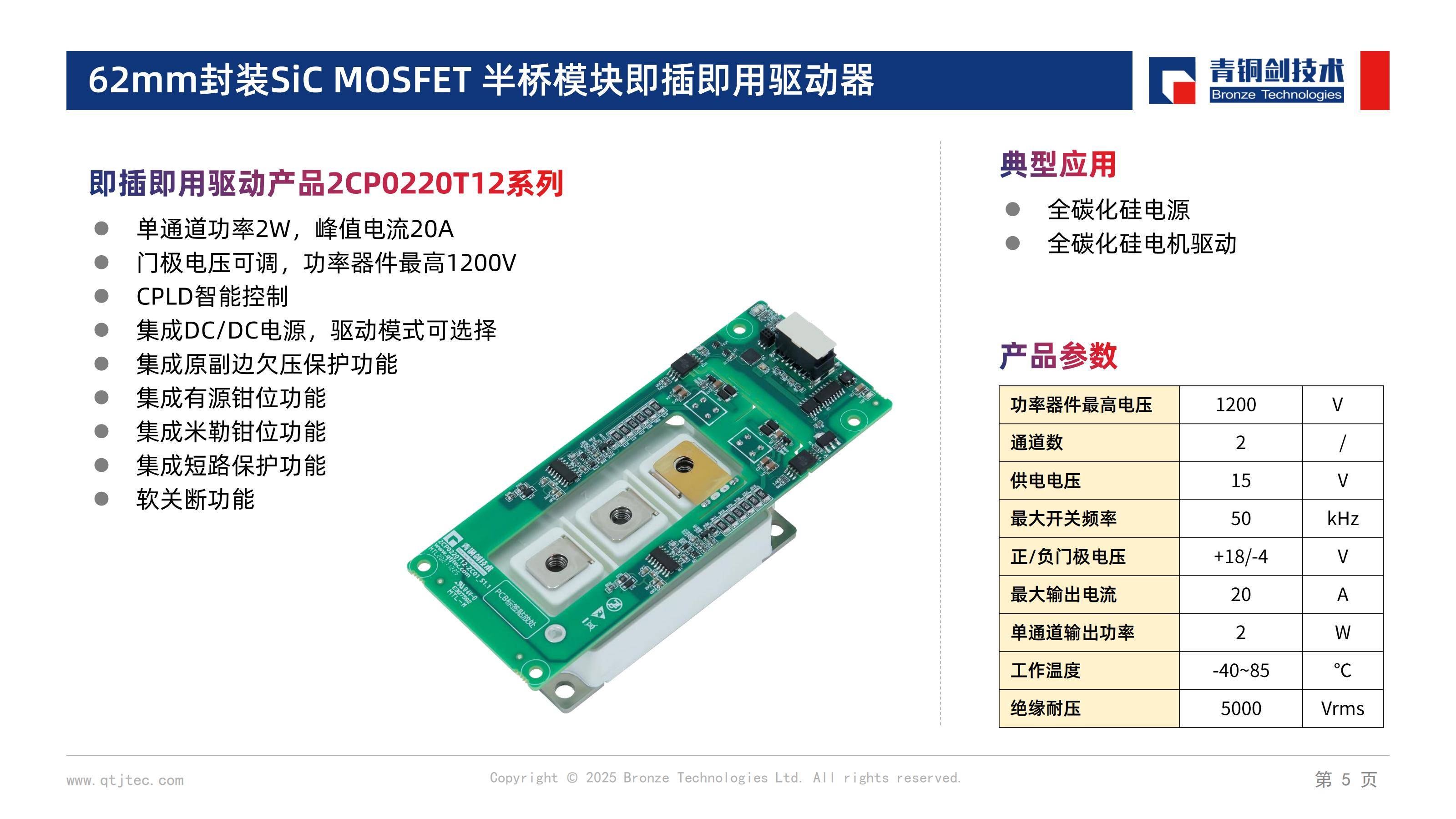

- 硬件组合 B(62mm封装): BMF540R12KHA3 (540A) + 2CP0220T12-ZC01 驱动板 (±20A)。

- 匹配逻辑: 隔离副边电流极大,540A模块(RDS(on)=2.2mΩ)可最大程度降低导通损耗。由于 QG 高达 1320nC,必须依靠 ±20A∼±25A 的强劲峰值电流驱动。

二、 多物理场系统级建模 (基于 Simulink / PLECS)

在进行系统仿真前,需将手册中的静态、动态及热力学图表转化为精确的仿真模型:

1. SiC 功率器件电热耦合建模

- 非线性导通模型: SiC 的导通电阻具有正温度系数。建立二维查表(LUT):例如 540A 模块在 25∘C 时 RDS(on)=2.2mΩ,在 175∘C 时升至约 3.8mΩ∼3.9mΩ。

- 体二极管压降预警: 必须在模型中引入高昂的体二极管压降特性(手册显示在 540A 时 VSD 典型值为 4.9V,最大 5.33V)。这是后续优化“死区时间”的关键依据。

- 开关损耗模型 (3D LUT): 将 Eon 和 Eoff 随 VDS,ID,RG 和 Tvj 变化的曲线导入仿真(例如 540A 模块在 800V 时,Eon≈37.8mJ, Eoff≈13.8mJ)。

- 热阻网络 (Cauer/Foster): 根据手册中的“瞬态热阻抗 Zth(j−c)”曲线建立物理热网络,输入结壳热阻 Rth(j−c)(如 0.077 K/W),用于仿真高频脉冲下的瞬态结温波动。

2. 驱动器行为学与保护逻辑建模

- 传输延迟与死区: 在仿真控制环路中加入 180ns∼500ns 的信号传输延迟(td(on) / td(off))。

- DESAT 短路保护与软关断: 模拟退饱和检测逻辑(VREF≈10V∼10.2V,响应时间 tsc≈1.7μs)。更关键的是,在注入短路故障仿真时,模型应模拟栅极电压以 2.1μs∼2.5μs 的斜率缓慢下降**(软关断,Soft Shutdown)**,以验证此时母排 Lσ⋅di/dt 电压尖峰是否在安全范围内。

三、 SST 架构设计与维度优化策略

通过高精度的“器件+驱动”模型,可以在仿真阶段针对 SST 架构进行以下深度的优化:

优化点 1:基于“驱动功率瓶颈”的极限开关频率 (fs) 寻优

SST 提升功率密度的关键是推高开关频率(缩小中/高频变压器体积),但频率受限于驱动板的 2W 单通道功率限制。

计算边界: Pdriver=QG×ΔVGS×fs

以 BMF540 模块为例,QG=1320nC,正常工作驱动电压摆幅 ΔV=18V−(−5V)=23V。

最大理论频率边界为:fs(max)=2W/(1320nC×23V)≈65.8kHz。

优化动作: 在仿真中,将 DAB 隔离级的频率扫描范围锁定在 20kHz - 50kHz(留有降额裕量),寻找“开关热损耗”与“纳米晶磁芯体积/损耗”的帕累托最优解。

优化点 2:避开“死区陷阱”——驱动模式与死区时间深度优化

- 核心痛点: 青铜剑 2CP0220/2CP0225 驱动板手册明确指出,在“半桥模式(Half-bridge Mode)”下,硬件自带的死区时间高达 3.2μs 。如果使用该模式,SiC 模块巨大的体二极管压降(∼5V)将在 3.2μs 的续流期间产生极其惊人的导通损耗,导致芯片迅速过热。

- 优化动作: 在控制架构设计中,强烈建议将驱动板配置为“直接模式(Direct Mode)” (处理 MOD 引脚电平)。由上位机(DSP/FPGA)进行精确的死区补偿控制,将死区时间压缩至 SiC 器件适宜的 300ns∼500ns ,大幅提升系统效率。

优化点 3:栅极电阻 (RG) 与“高级有源钳位”的博弈设计

- 核心痛点: 减小关断电阻 RG(off) 能显著降低关断损耗 Eoff,但极高的 di/dt 配合母排杂散电感 Lσ 会产生致命的电压过冲。

- 优化动作: 得益于青铜剑驱动板(如 2CP0225Txx)集成了高级有源钳位(Advanced Active Clamping,动作阈值如 1020V/1320V) 。在仿真中,您可以大胆地调低 RG(off)(如选用 1.5Ω∼3.1Ω 之间)以压榨最高效率;并通过满载切断仿真验证:即便存在过冲,瞬态电压也会被驱动板的有源钳位电路死死钳制在安全阈值(如 1020V)内,从而在效率和绝缘应力之间实现完美折中。

优化点 4:DAB 零电压开通(ZVS)边界的控制优化

- 优化动作: 提取 SiC 手册中的 Eoss 数据(例如 800V 时输出电容储能约为 509μJ)。在仿真中调整 DAB 变压器的漏感 Lk,并引入**双重移相(DPS)或三重移相(TPS)**控制策略。确保在轻载工况下,漏感电流仍足以在 300ns 死区时间内抽干对管的 509μJ 电荷,实现全负载范围的 ZVS,以此彻底消除 Eon 带来的热负担。

总结:

利用基本半导体的高性能 1200V SiC 模块,搭配青铜剑集成了“软关断 + 有源钳位 + 米勒钳位”的高级智能驱动板,是构建兆瓦级 SST 系统的黄金组合。在研发过程中,利用“直接模式”压缩死区时间、基于驱动功率推算频率上限、以及借助有源钳位压榨极低 RG 效率,将是您优化 SST 架构设计的核心发力点。

)

)

)

)

)

)

)

在情人节当天通过Instagram分享了一组甜蜜的自拍拼图,证实了自己已名草有主。虽然他没有透露女友的身份,但这位2月13日刚满25岁的加拿大演员表示,自从“我的2000)

)

)

)

)

)